이진수 덧셈

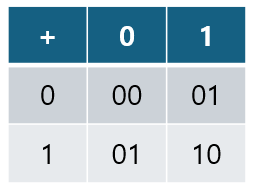

십진수와 이진수에서 중요한 차이점 중 하나는 이진수에서 훨씬 간단한 표를 사용한다는 점이다.

여러분이 돌고래 사회에서 자랐다면 위의 표를 학교에서 배웠을 테고 아래와 같은 노래를 불렀을 것이다.

0 더하기 0은 0.

0 더하기 1은 1.

1 더하기 0은 1.

1 더하기 1은 0이고, 자리올림 1.

다음과 같이 앞의 표에서 앞자리에 0을 추가해서 2비트 값으로 표현해 볼 수 있다.

이진법에서 2는 존재하지 않는다. 2가 된다면 이는 자리올림을 하라는 신호이다.

숫자 10은 허상이다

숫자 10의 고유성은 없다고 생각하자 숫자를 나타내는 digit이라는 영어 단어는 라틴어 digitus에서 유래된 단어이다. 라틴어 digitus는 "손가락 또는 발가락"을 의미한다. 옛 시절부터 손가락, 발가락

jettstream.tistory.com

숫자 10에 대한 글이다. 참고하면 좋다.

다음과 같이 앞의 표에서 앞자리에 0을 추가해서 2비트 값으로 표현해 볼 수 있다.

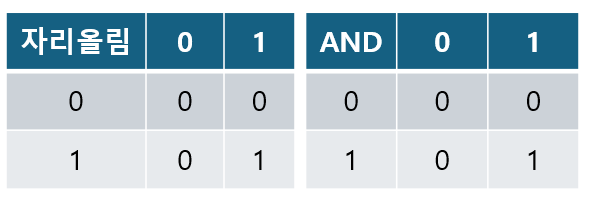

위에서 보이는 것처럼 한 비트의 두 이진수를 더하면 두 비트가 되며, 각각의 합(sum) 비트와 자리올림(carry) 비트라고 한다. 이제 이진수의 덧셈표를 두 개의 표로 나누어 보자.

첫 번째 표는 합 비트에 대한 표이다.

두 번째는 자리올림 비트에 대한 표이다.

우리가 만들려는 이진수 덧셈기도 합과 자리올림을 각각 처리하도록 만들 것이기 때문에 이진수의 덧셈을 위와 같이 나누어 생각하는 것이 편하다. 이진수 덧셈기를 만들기 위해서는 위에 설명한 동작들을 수행하는 회로를 설계하면 되는 것이다.

이제 이를 논리 게이트로 옮겨보자.

AND 게이트를 이용하여 두 이진수 간의 덧셈에 대한 자리올림 비트를 계산해 낼 수 있다.

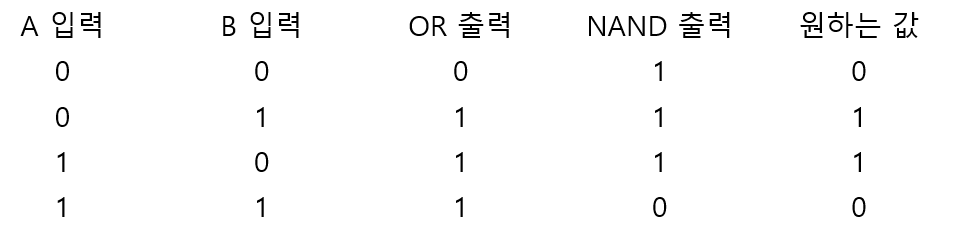

이제 합 비트를 계산할 수 있는 논리 회로를 찾아내면 된다.

우선 합(sum) 부분의 결과에서 오른쪽 아랫부분을 제외하면 OR 게이트의 결과와 같다는 것을 알 수 있다.

또한 왼쪽 윗부분만 제외하면 NAND 게이트의 결과와 값이 같다.

그렇다면 OR와 NAND 게이트에 같은 입력을 주고 잘 연결해보면 뭔가 나오지 않을까요?

이 표를 보면 OR 게이트의 연결과 NAND 게이트의 결과가 모두 1인 경우에만 값이 1이 되도록 한다면 우리가 원하는 결과가 되는 점을 알 수 있다. 이제 두 게이트의 출력을 AND 게이트의 입력으로 연결하면 된다.

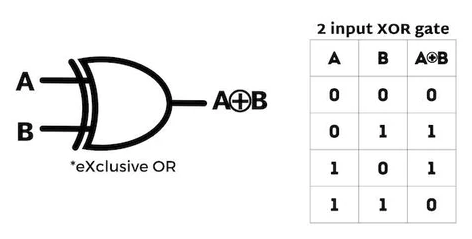

이 회로에는 이름이 있다. 입력 A 혹은 B가 1인 경우에는 출력이 1이 되지만, 두 입력 모두가 1이 되는 경우에는 0이 되기 때문에 상호 배제적(Exclusive)인 OR 게이트, 짧게 XOR 게이트라는 이름을 가지고 있다.

이제 정리해보면, 두 이진수를 더하면 합 비트와 자리올림 비트가 발생한다. 이는 다음의 두 논리 게이트를 이용해서 결과를 얻을 수 있다.

- 합 비트 - XOR 게이트

- 자리올림 비트 - AND 게이트

'반가산기(Half Adder)'라는 이름이 붙은 온전한 이유가 있다. 분명 이 가산기도 한 비트짜리 두 이진수를 더해서 합 비트와 자리 올림 비트를 만들어낸다. 하지만 대부분의 이진수가 한 비트만으로 이루어진 것은 아니다. 반가산기의 단점은 바로 아랫자리에서 덧셈을 통해 올라온 자리올림을 처리할 수 없다는 것이다.

두 반가산기를 합쳐서 '전가산기(Full Adder)'를 만들고, 이를 통해 아랫자리에서 올라온 자리올림을 처리해 보자.

다음의 표에는 전가산기에서 발생 가능한 모든 입력에 대하여 만들어질 수 있는 모든 출력을 요약한 것이다.

자. 이제 다 된 거 같습니다.

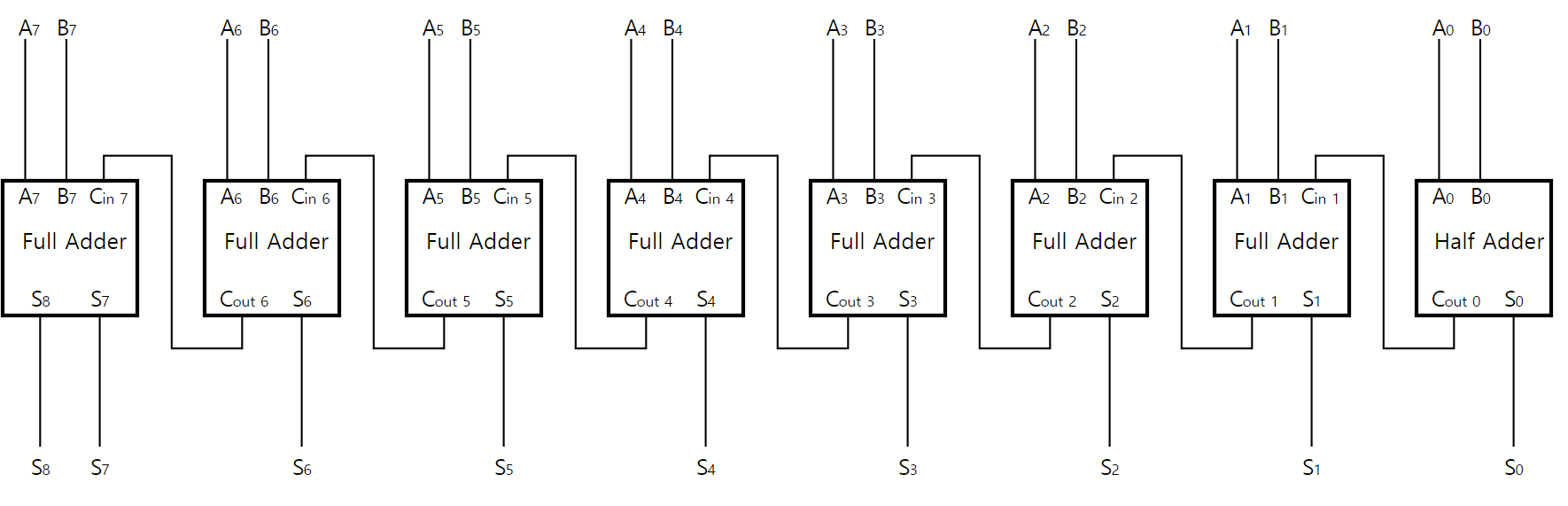

여덟 개 전가산기에서의 자리올림 출력이 그 윗자리의 자리올림 입력으로 제공됨으로써 여덟 개의 전가산기를 다음과 같이 묶어서 표현할 수 있다.

만들어진 8비트 덧셈기를 만들고 나면, 이제 다른 것도 만들 수 있다. 만들어진 8비트 덧셈기 두 개를 직렬로 배치하면 16비트 숫자 두 개를 더 할 수도 있다.

순차적으로 이진수 계산부터 16비트 계산기까지 만들어보았다.

함께 읽으면 좋은 글

전기로 덧셈을 표현하는 반가산기, 전가산기

덧셈을 해보자 CPU가 덧셈을 계산하는 방법에 대해서 알아보도록 하자 CPU는 내부적으로 이진수를 이용해서 모든 숫자를 계산한다. 아래와 같은 계산을 진행한다고 생각해 보자. 해당 계산을 위

jettstream.tistory.com

이진수 뺄셈을 해보자!

이제 뺌셈을 해보자 뺄셈은 기본적으로 덧셈과는 다르게 빌림수(borrow)가 발생한다. 253 -176 =??? 이 문제를 풀기 위해 오른쪽 자리에서부터 시작하도록 하자. 우선 6은 3보다 크기 때문에 윗자리의

jettstream.tistory.com

출처

CODE (블랙 에디션) - 예스24

23년 만에 돌아온 컴퓨터 공학 분야의 필독서!20년이 넘는 세월 동안 컴퓨터 공학 분야의 필독서로서 많은 독자를 열광하게 만든 《CODE》가 새로운 컴퓨팅 시대에 맞춰 개정되었습니다. 컴퓨터

www.yes24.com

'프로그래밍' 카테고리의 다른 글

| 중위 표기법을 후위 표기법으로 변환하기 (0) | 2024.04.22 |

|---|---|

| 이진수 뺄셈을 해보자! (1) | 2024.02.07 |

| 추상 자료형(Abstract Data Type, ADT)란 무엇인가? (0) | 2024.01.25 |

| SuperSocket Custome 프로토콜 정의 (1) | 2024.01.05 |

| 비주얼 스튜디오 코드로 UML 그리기 (0) | 2023.12.19 |

댓글